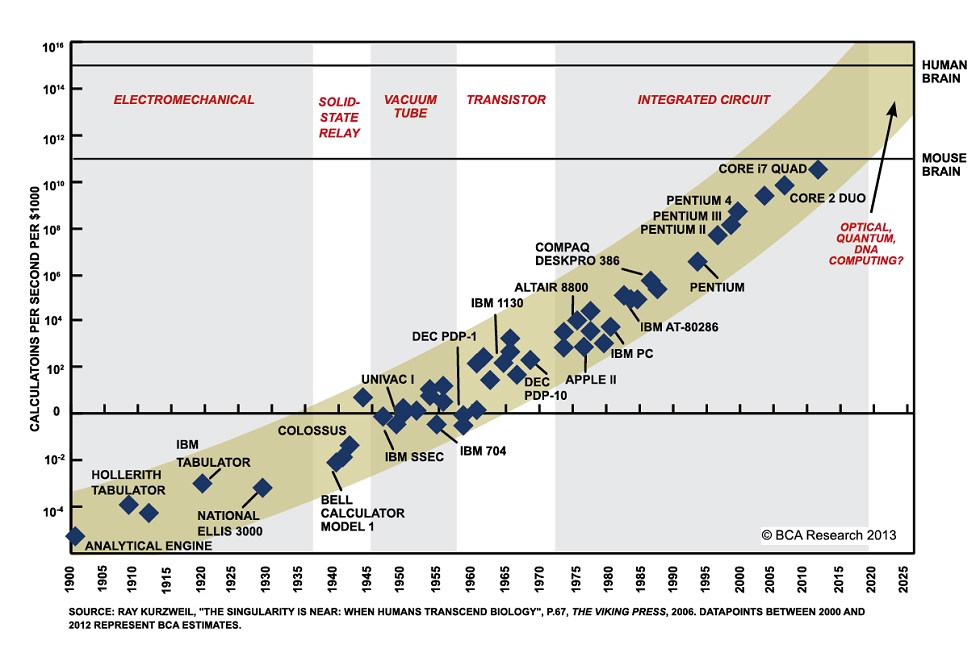

تحقیقات گوردون مور، بنیانگذار اینتل در دهه 1960 میلادی نشان میداد که تعداد ترانزیستورهای درون مدار مجتمع در هرسال دوبرابر میشود. به همین دلیل نیز کلمه قانون به ابتدای نام مور اضافه شد تا تعداد ترانزیستورها در هرسال را شمارش کند، این قانون را امروزه، قانون مور مینامند. هماکنون، شرکتهای بزرگی مثل TSMC و سامسونگ درحال تولید و استفاده از تراشههای پردازشی 7 نانومتری هستند و در سال آینده نیز تراشههای 5 نانومتری به مرحله تولید انبوه میرسند.

اما اصلیترین سوال درباره این موضوع به بقا قانون مور مربوط میشود و باید منتظر ماند و دید که آیا این قانون روزی نقض خواهد شد یا خیر؟ سال گذشته نیز سامسونگ نقشه راه خود را برای تولید تراشههای 3 نانومتری تا سال 2022 میلادی فاش کرد و TSMC نیز تدارکات را برای تولید این نوع از تراشهها آماده میکند. بنابراین، میتوان انتظار داشت که تراشههای 3 نانومتری نیز در سالهای آینده در تلفنهای هوشمند تعبیه خواهند شد.

مهمترین دلیل برای افزایش تعداد ترانزیستورهای یک تراشه پردازشی، به قدرت و انرژی بیشتر آن مربوط میشود. هرچهقدر تعداد ترانزیستورهای بیشتری در داخل یک آیسی (IC) قرار گیرند، تراشه موردنظر از قدرت زیادی برخوردار خواهد بود.

به عنوان مثال، پردازنده A4 شرکت اپل که در آیفون 4 مورد استفاده قرار گرفته بود، توسط فرآیند 45 نانومتری تولید میشد. اکنون شما میتوانید این تراشه را با جدیدترین تراشه اپل، یعنی A12 Bionic مقایسه کنید که در فرآیند 7 نانومتری به تولید رسیده و در آیفونهای 2018 مورد استفاده قرار گرفته است.

شاید جالب باشد که بدانید تراشههای 5 نانومتری که سال آینده به تولید میرسند، در هر میلیمتر مربع دارای 171.3 میلیون ترانزیستور خواهند بود.

TSMC معتقد است که قانون مور هنوز نمرده!

گادفری چنگ، مدیر بازاریابی بینالمللی TSMC، هفته گذشته در وبلاگ این شرکت درباره قانون مور صحبت کرد. چنگ درباره این موضوع میگوید که TSMC در طول سالهای آینده به نوآوریهای خود درباره کاهش اندازه ترانزیستورها ادامه خواهد داد و سعی میکند تا بیشترین تعداد ترانزیستور را در یک مکان قرار دهد.

TSMC یکی از بزرگترین کارخانههای ریختهگری صنایع نیمههادی در جهان است که تراشههای طراحیشده توسط شرکتهای بزرگی مانند اپل، هواوی و کوالکام را تولید میکند.

چنگ خاطرنشان کرد: “از آنجایی که قانون مور برپایه افزایش تراکم فضای تراشهها بنا شده است، کارهای مختلفی را میتوان برای جادادن ترانزیستورهای بیشتر در مدارهای مجتمع انجام داد. بهترین راه برای انجام این کار، بهبود فرآیند قراردادن ترانزیستورها در فضای فیزیکی چیپست است. دومین احتمال برای جلوگیری از کمبود فضای تراشه، اجتناب از ماده سیلیکون و استفاده از مواد دوبعدی است. TSMC به دنبال چنین مادهای در جدول تناوبی عنصرها بوده تا با قراردادن ترانزیستورهای برروی هم بهجای کنار هم گذاشتن آنها از ترانزیستورهای بیشتری در چیپستها بهره گیرد.”

انتظار داریم که هفته آینده در سمپوزیوم Hot Chips سخنان بیشتری را در رابطه با قانون مور و تراشههایی با کارایی بالا بشنویم. این سمپوزیوم روز سهشنبه در شهر پالو آلتو کالیفرنیا آمریکا با سخنرانی دکتر فیلیپ وانگ، معاون ارشد بخش تحقیقات شرکت TSMC آغاز خواهد شد. عنوان بحث فیلیپ وانگ درباره دشواریهای بعدی شرکتهای سازنده تراشه خواهد بود. البته اصلیترین دشواری به تلفنهای قدرتمندتر و با کارایی بالا مربوط میشود.

لطفا مطلبی در مورد این ترانسیستورها و اندازهای آنها بنویسید

چشم. به ادمین سایت اطلاع میدم تا در صورت تایید دوستان مطلبی رو در این باره تهیه کنند.