کمپانی تایوانی TSMC از فرآیند تولید نوآورانه 1.6 نانومتری خود برای تراشهها رونمایی کرد. این فناوری، شبکه توزیع انرژی در پسزمینه را شامل شده و بازدهی انرژی و تراکم ترانزیستورها را بیش از پیش ارتقاء میدهد.

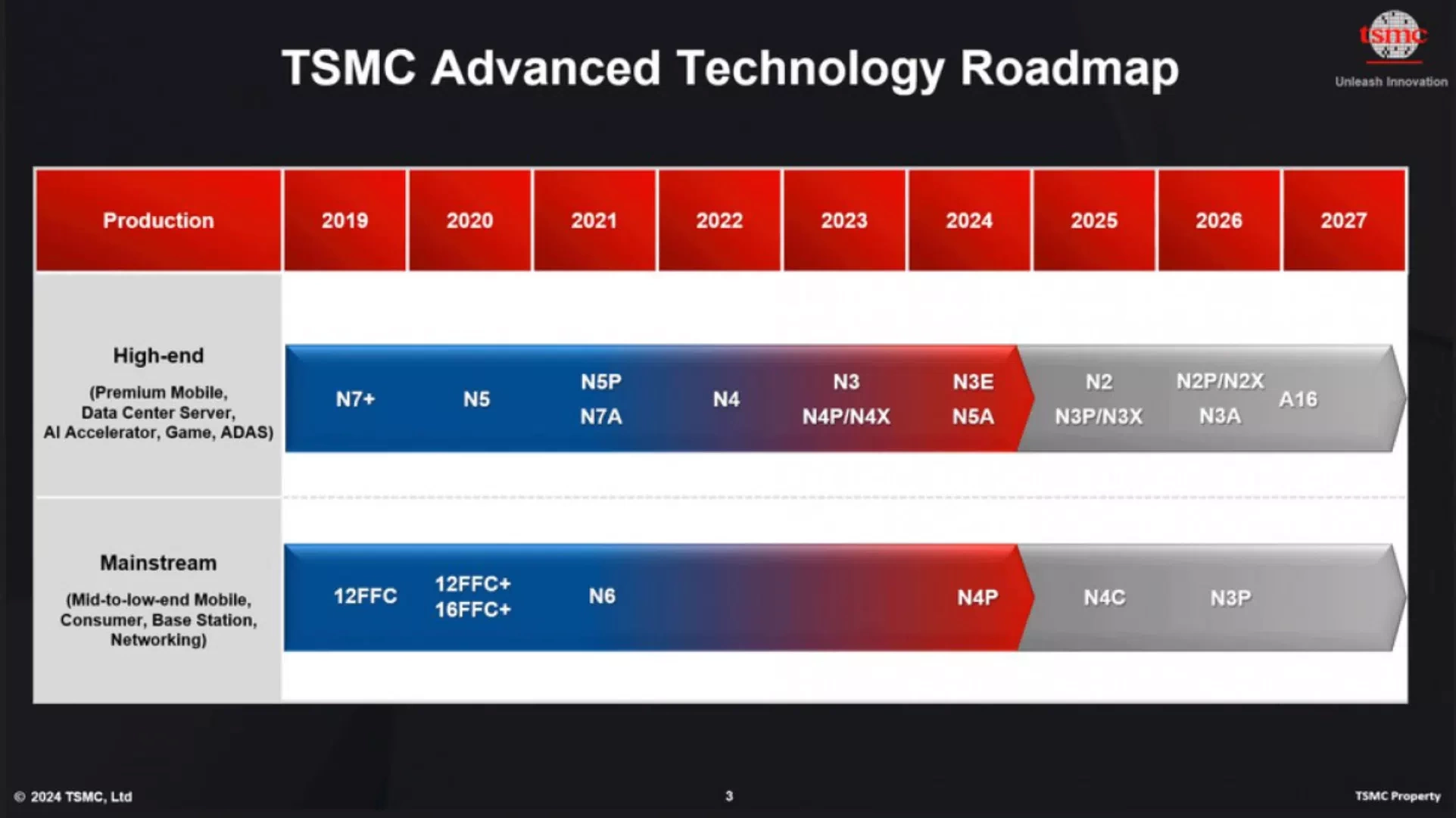

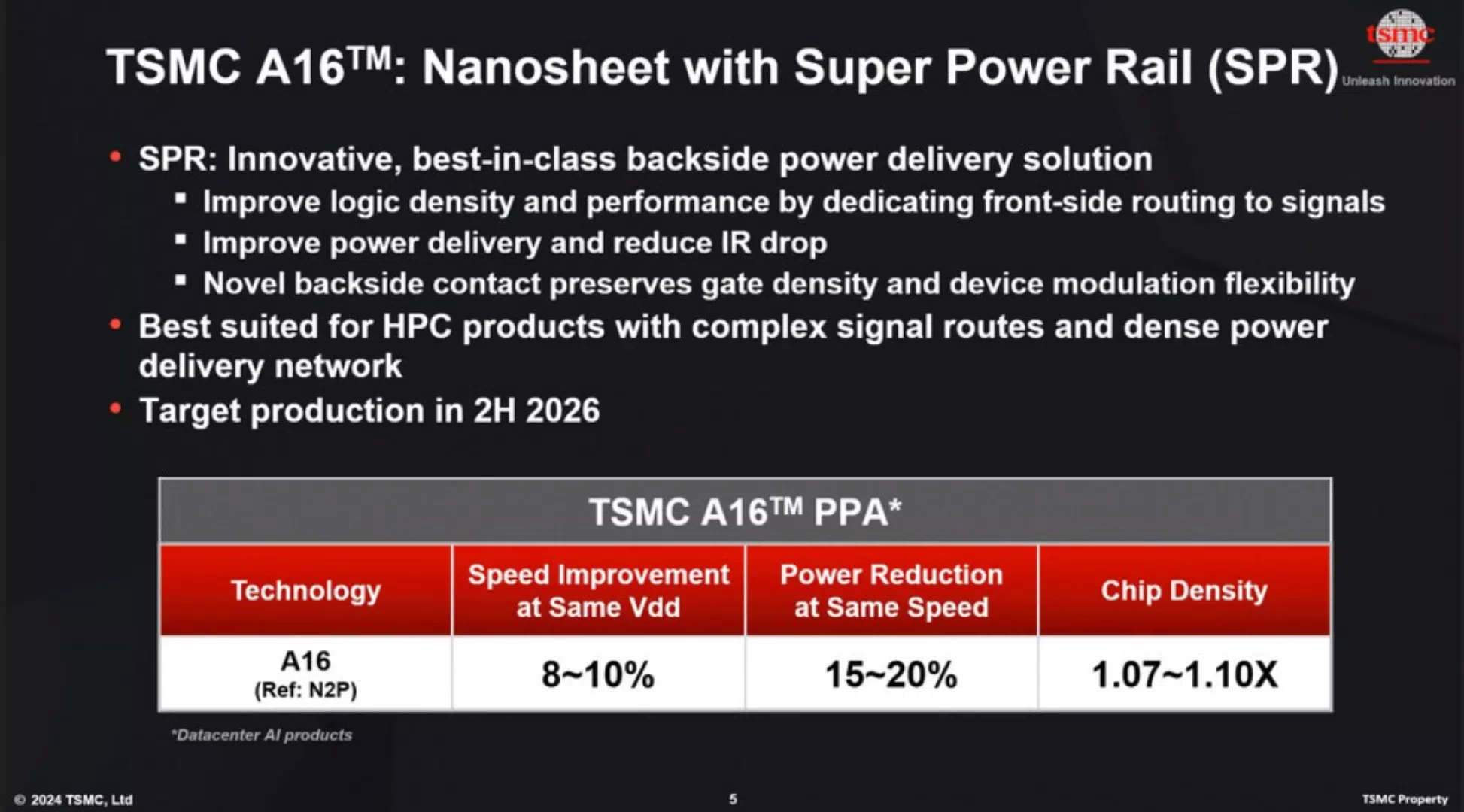

فرآیند 1.6 نانومتری معرفی شده دقیقا همانند معماریهای جدید N2P، N2 و N2X بر پایه گره فرآیندی 2 نانومتری بنا شده است. فرآیند جدید به تنهایی امکان دسترسی به 10 درصد فرکانس بیشتر در ولتاژ مشابه و کاهش حداکثر 20 درصدی میزان مصرف انرژی در فرکانس و پیچیدگی یکسان را فراهم میکند.

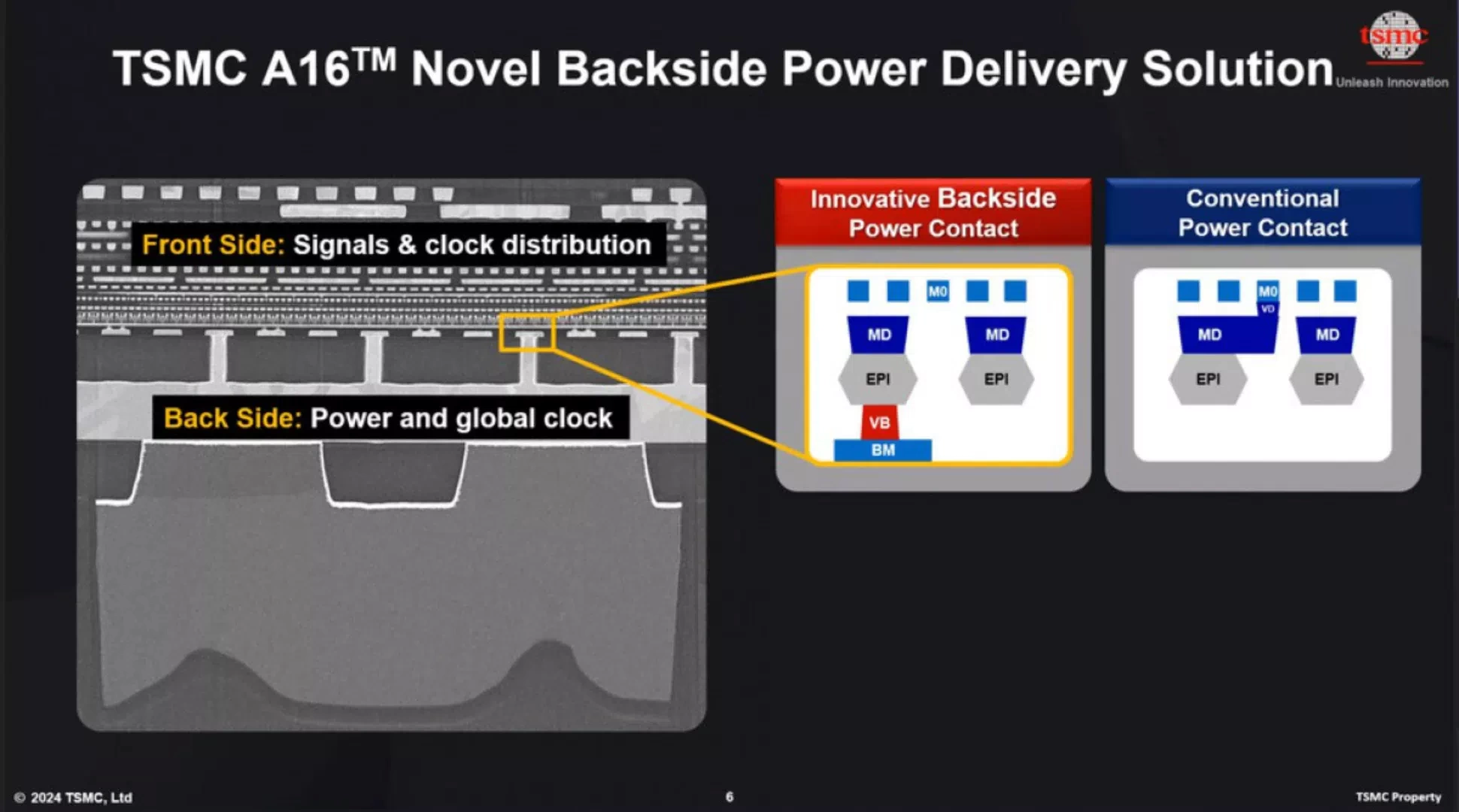

فرآیند جدید 1.6 نانومتری بسته به طراحی تراشه میتواند تا 10 درصد ترانزیستورهای بیشتر را در خود جای دهد. شبکه تحویل توان در پسزمینه احتمالا یکی از جوانب چشمگیرتر تراشههای آینده بهشمار میرود؛ چرا که این ویژگی به ارتقاء چگالی ترانزیستور و بهبود انتقال توان کمک کرده و به نوبه خود بر عملکرد تاثیر میگذارد.

کمپانی TSMC در توضیحات خود به ویژگی Super Power Rail (SPR) اشاره نموده است. این مولفه نوعی بستر برای اتصال تراشه به منبع انرژی محسوب میشود.

شبکه تحویل انرژی پسزمینه عمدتا برای پردازندههای هوش مصنوعی و HPC که نیازمند سیمکشی سیگنال پیچیده و شبکههای متراکم قدرت هستند؛ مفید واقع میشود.

جدول زمانی تولید برای 6 ماهه دوم سال 2026 برنامهریزی شده است. چنانچه همه چیز مطابق برنامه به پیش برود؛ در اینصورت اولین محصولات مصرفی با تراشههای 1.6 نانومتری در سال 2027 عرضه خواهند شد.